# Pavlo Bazilinskyy Multi-core Insense

University of St Andrews

June 2013

# ABSTRACT

This project set out to investigate the benefits of using private heaps for memory management and static thread placement for optimising performance and cache usage. For this study, Insense, which is a component-based programming language developed in the University of St Andrews that abstracts over complications of memory management, concurrency control and synchronisation, was used (Dearle et al. 2008). Two memory management schemes are under investigation: use of a single shared heap and use of multiple private heaps. Further, three thread placement schemes are designed and implemented: 1) even distribution among cores; 2) placing all components on a single core; 3) locating Insense components based on frequency of inter-component communication.

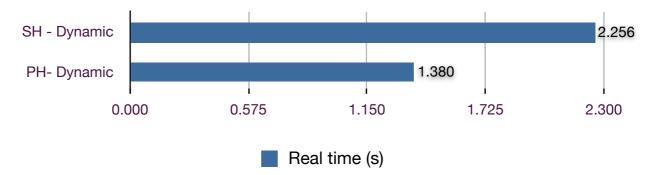

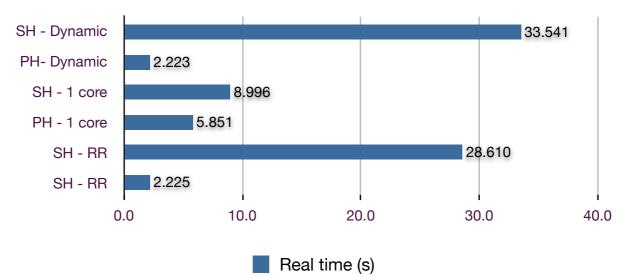

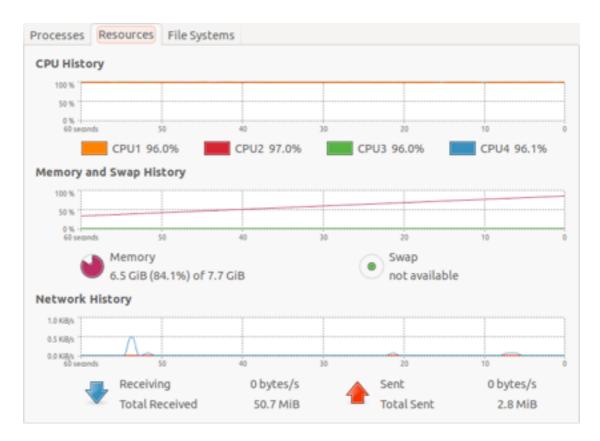

Furthermore, several elements of this investigation are worth emphasizing. With regard to allocation and deallocation of memory taking place in component instances running on different cores, the efficiency of using a private heap for each component resulted in speedup by a factor of 16. Then, utilising private heaps reduces a number of L1 cache misses by ~30%. Distributing components over cores according to communication pattern, for the most part performed similar to allowing the OS to perform thread placement dynamically according to load balance. In cases where no exchange of data between components takes place, static placement outperformed because there is no computation which may make load balancing dynamic placement of threads under control of the OS difficult. In this case, the static placement scheme was faster than dynamic balancing by a factor of 2.4.

# DECLARATION

I declare that the material submitted for assessment is my own work except here credit is explicitly given to others by citation or acknowledgement. This work was performed during the current academic year except where otherwise stated.

The main text of this project report is 19,991 words long, including project specification and plan.

In submitting this project report to the University of St Andrews, I give permission for it to be made available for use in accordance with the regulations of the University Library. I also give permission for the title and abstract to be published and for copies of the report to be made and supplied at cost to any bona fide library or research worker, and to be made available on the World Wide Web. I retain the copyright in this work.

# ACKNOWLEDGEMENTS

Words cannot describe my deep appreciation to my supervisor Jonathan Lewis, who was always there to listen to my ideas and who was patient enough to often describe the same concept to me for the 2<sup>nd</sup>, 3<sup>rd</sup> and sometimes even 4<sup>th</sup> time. He was always available whenever I needed him, and his positive attitude towards this project encouraged me to not give up, especially during the first half of my work, when I would very often have entered a vicious circle, in which I could not have achieved desired results for days or even weeks.

I would also like to express my gratitude to Professor Alan Dearle, who is one of the creators of Insense language. Me, Jonathan, and him spent countless hours discussing theoretical aspects of the project, which gave me numerous sleepless nights. He had faith in me and it helped me go forward and motivated me greatly. Also, thank you enormously for showing me power of taking notes with my iPad.

Special thanks, to my parents, my grandmother, and my whole family who if it were not for them, I would not be here submitting this project. Even though we have been separated by thousands of miles for now four years, I always had continuous support from their side, which proved to be more than enough to help me make it to the end, without regrets.

# CONTENTS

| 1 INTRODUCTION                                    | 1  |

|---------------------------------------------------|----|

| 1.1 Dissertation structure                        | 1  |

| 2 OBJECTIVES                                      | 2  |

| 3 CONTEXT SURVEY                                  | 3  |

| 3.1 Multi-core Systems                            | 3  |

| 3.1.1 Memory Cache in Multi-core Systems          | 4  |

| 3.2 Overview of Insense Language                  | 5  |

| 3.2.1 Components and Channels in Insense          | 7  |

| 3.2.2 Data Types                                  | 10 |

| 3.3 Memory Management in C Language               | 11 |

| 3.4 Utilising Private Heaps for Memory Management | 12 |

| 3.5 Thread Affinity                               | 14 |

| 4 SOFTWARE ENGINEERING PROCESS                    | 14 |

| 4.1 Project Plan                                  | 15 |

| 5 REQUIREMENTS SPECIFICATION                      | 16 |

| 5.1 Functional Requirements                       | 16 |

| 5.2 Non-functional Requirements                   | 17 |

| 6 ETHICS                                          | 17 |

| 7 DESIGN                                          | 17 |

| 7.1 Design of Multi-core Insense                  | 18 |

| 7.1.1 Components                                  | 18 |

| 7.1.2 Channels                                    | 18 |

| 7.1.3 Program Entry Point                         | 19 |

| 7.1.4 Memory Management & Garbage Collection      | 20 |

| 7.2 Data Placement Schemes                        | 21 |

| 7.2.1 Shared Heap                                 | 21 |

| 7.2.2 Private Heaps                               |    |

| 7.2.3 Data Placement and Potential Cache Misses   | 23 |

| 7.3 Thread Placement Schemes                      | 27 |

| 7.3.1 Dynamic Placement                           |    |

| 7.3.2 Static Placement                            |    |

| 8 IMPLEMENTATION                                  |    |

| 8.1 Base Unix Implementation                                         | 33            |

|----------------------------------------------------------------------|---------------|

| 8.1.1 Components                                                     | 34            |

| 8.1.2 Arrays                                                         | 37            |

| 8.1.3 Channels                                                       |               |

| 8.1.4 Program Entry Point                                            | 43            |

| 8.1.5 Memory Management & Garbage Collection                         | 44            |

| 8.1.6 Thread-safe List                                               | 46            |

| 8.1.7 Build System                                                   | 47            |

| 8.2 Data Placement Schemes                                           | 49            |

| 8.2.1 Shared Heap                                                    | 52            |

| 8.2.2 Private Heaps                                                  | 53            |

| 8.2.2.1 Creation of a New Private Heap                               | 54            |

| 8.2.2.2 Allocation and Deallocation of Memory within the Privat      | e Heaps55     |

| 8.3 Thread Placement Schemes                                         | 59            |

| 8.3.1 Dynamic Placement                                              | 59            |

| 8.3.2 Static Placement                                               | 60            |

| 8.3.2.1 Even Distribution of Threads Among Cores                     | 62            |

| 8.3.2.2 Static Placement of Threads to a Single Core                 | 63            |

| 8.3.2.3 Static Placement of Threads Based on Communication           | 63            |

| 9 EXPERIMENTS                                                        | 63            |

| 9.1 Effects of Memory Management Schemes on Allocation and Deallocat | ion of Memory |

|                                                                      | 64            |

| 9.1.1 Design of Experiments                                          | 64            |

| 9.1.2 Program Used                                                   | 65            |

| 9.1.3 Experimental Results                                           | 65            |

| 9.1.4 Discussion of Results                                          | 66            |

| 9.2 Effects of Memory Management Schemes on Cache Usage              | 68            |

| 9.2.1 Design of Experiments                                          | 68            |

| 9.2.2 Program Used                                                   | 69            |

| 9.2.3 Experimental Results                                           | 69            |

| 9.2.4 Discussion of Results                                          | 70            |

| 9.3 Effects of Thread Placement and Communication Between Component  | ts on         |

| Performance                                                          | 71            |

| 9.3.1 Design of Experiments                                          | 71            |

| 9.3.2 Programs Used                                                       | 72            |

|---------------------------------------------------------------------------|---------------|

| 9.3.3 Experimental Results                                                | 73            |

| 9.3.4 Discussion of Results                                               | 77            |

| 0 CONCLUSIONS AND FURTHER WORK                                            | 78            |

| 1 BIBLIOGRAPHY                                                            | 80            |

| APPENDICES                                                                |               |

| APPENDIX 1: List of Figures                                               | 84            |

| APPENDIX 2: Gantt Chart for the Project                                   | 89            |

| APPENDIX 3: Instruction on Executing Insense Programs                     | 90            |

| APPENDIX 4: Creation of a New Component                                   | 90            |

| APPENDIX 5: Deallocation of Memory for Private Heaps                      | 92            |

| APPENDIX 6: Test_alloc Program Used to Evaluate Effects of Using Multiple | ple Heaps for |

| (De-)allocation of Memory                                                 | 93            |

| APPENDIX 7: Test_cache Program Used to Evaluate Effects of Memory Ma      | anagement     |

| Schemes on Cache Usage                                                    | 93            |

| APPENDIX 8: Programs Used to Evaluate Effects of Thread Placement and     | ł             |

| Communication Between Components on Performance                           | 94            |

| Appendix 8.1: "Sender - Receiver" Scheme                                  | 94            |

| Appendix 8.2: "Client - Server" Scheme                                    | 95            |

| Appendix 8.3: "Dispatch - Worker" Scheme                                  | 97            |

| Appendix 8.4: "No communication" Scheme                                   | 98            |

| APPENDIX 9: Real, User, and System Time of Running Experiments            | 99            |

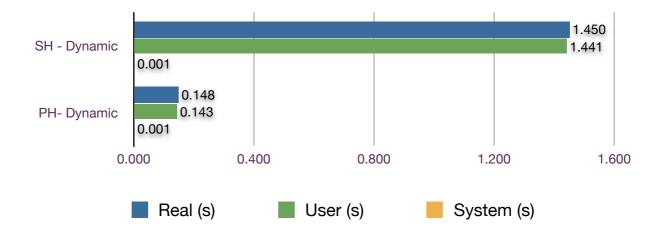

| Appendix 9.1: Experiment with (De-)allocation of Memory, 1 Compone        | nt99          |

| Appendix 9.2: Experiment with (De-)allocation of Memory, 4 componer       | nts100        |

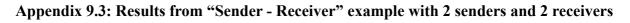

| Appendix 9.3: Results from "Sender - Receiver" example with 2 senders     | s and 2       |

| receivers                                                                 | 100           |

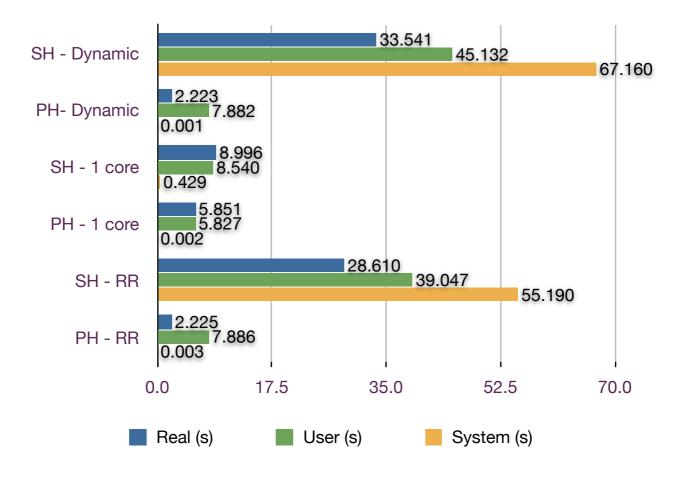

| Appendix 9.4: Results from "Client - Server" example                      | 101           |

| Appendix 9.5: Results from "Dispatch - Worker" example                    | 102           |

| APPENDIX 10: Ethics approval form                                         | 104           |

| APPENDIX 11: Output of Cachegrind for the test_cache program              | 109           |

| Appendix 11.1: Shared Heap - Dynamic                                      | 109           |

| Appendix 11.2: Private Heaps - Dynamic                                    | 109           |

| Appendix 11.3: Shared Heap - 1 core                                       | 109           |

| Appendix 11.4: Private Heaps - 1 core                                     | 110           |

| Appendix 11.5: Shared Heap   | - Round-Robin   | 110 |

|------------------------------|-----------------|-----|

| Appendix 11.6: Private Heaps | s - Round-Robin | 110 |

#### **1 INTRODUCTION**

Insense is a component-based programming language developed in the University of St Andrews that abstracts over complications of memory management, concurrency control and synchronisation, and separates application software from the hardware and the operating system (OS). Insense applications are constructed as collections of software components that communicate with each other by using typed, directional, synchronous channels. A component may contain updatable locations that may only be accessed by code defined in the component. Each component is a unit of concurrent computation. The language is mainly used in wireless sensor networks (WSN). However, researchers behind Insense have been speculating about porting it to multi-core systems. (Dearle et al. 2008)

Many multi-core operating systems provide mechanisms for load-balancing thread placement on cores. Dynamic memory is commonly allocated on a single large heap shared by all threads and processes running on the OS. However, such approaches may not always be the best ones for a given programming language on multi-core systems.

This project focuses on investigating benefits of utilisation of private (small) heaps for memory management and static thread placement for optimising efficiency and performance of applications running on multi-core systems. The base implementation of the project involves porting the language to the Unix-based Scientific Linux operating system. Three main objectives were set for this project.

#### **1.1 Dissertation structure**

The remainder of this dissertation is structured as follows: Chapter 2 outlines objectives that were set for this project. Chapter 3 surveys the context applicable to this project and includes a brief overview of relevant multi-core systems and the Insense programming language. Chapters 4 and 5 give a brief description of software engineering principles applied in the project and list functional and non-functional requirements that were set. Chapters 6 deals with ethical concerns. Chapter 7 summarises design process that was undertaken in the project and lists design decisions that were taken. Then, Chapter 8 first describes how Insense was adjusted to run on Unix-based systems that operate with multiple cores, then it gives a description of the main work performed on implementing schemes for memory management

and thread placement described in Chapter 7. Chapter 9 introduces experiments that were performed to test implemented memory management and thread placement schemes and describes achieved results. Lastly, Chapter 10 sums up what was accomplished and lists suggestions for future work.

#### **2 OBJECTIVES**

The main objectives of this project are to investigate efficient memory management and thread placement schemes for Insense on multi-core systems. To this end, a new Insense implementation for multi-core, Unix systems will be designed, implemented, and tested. This is an arduous undertaking in its own right because it involves creating a new version of the Insense language runtime (written in C) and modifying the compiler as well (written in Java). Some time must also be spent to understand the language, current runtime, and the InceOS and Contiki OS for which there is limited documentation.

Experimentation will then be used to establish which schemes are more efficient. Two memory management schemes are under investigation: use of a single shared heap and utilisation of multiple private heaps. When a single heap is used, it is anticipated that inefficiencies in cache and concurrent access to the shared heap from multiple threads may impact on performance. The research aims to investigate such effects and the effect of using multiple private heaps that are allocated to component instances or cores.

Further, three thread placement schemes are under investigation. One is based on static placement, where Insense components are distributed evenly among cores. Then, the scheme where all components are placed on a single core. The third scheme involves placing Insense components on cores based on certain properties that they have (e.g. frequency of communicating with other components). Results retrieved from experimenting with these three schemes will be compared to default behaviour of Unix-based systems where load balancing is performed via live migration of threads to different cores. Differences in performance of these approaches will be investigated.

Moreover, strong encapsulation of components in Insense applications may be advantageous for multi-core systems. The fact that Insense components are strongly encapsulated implies that they cannot share memory references to the component state. Information<sup>1</sup> can only be exchanged between components using channel abstraction. This feature of Insense can be tested by performing comparative analysis of solutions to a simple problem executed in Insense and a control language, for example, C, where direct access to shared memory from multiple threads can be exploited in the parallel algorithm. Retrieving this experimental data was set as the third, optional, goal of the project.

# **3 CONTEXT SURVEY**

#### 3.1 Multi-core Systems

The first member of the x86 mircroprocessor family was created as early as in 1978 when the Altair 8086 processor was designed (Gove 2011). Since then the world has seen a number of improvements in performance of central processing units (CPUs). The most notable improvement has been gain in speed of processors have come from increasing the clock speed (frequency at which a processor is running). The 8086 processor was functioning at around 5 MHz, today readings of clock speed can go as high as 5.5GHz (Halfacree 2012).

Furthermore, improvements in performance of processors were achieved by exploiting instruction-level parallelism - simultaneously performing multiple operations in a computer program (Hennessy 2007). Processors that use instruction-level parallelism have the ability to issue numerous instructions concurrently. In their pipelines, instructions are pre-fetched, split into sub-components and executed out-of-order (Schauer 2008). The Pentium IV CPU released in 2000 was one of the last and the most powerful single-core processors ("*Intel Introduces*" 2000). The "Prescott" and "Cedar Mill" cores from Pentium IV family featured as as many as 31 stages in their pipelines, the longest in the history of mainstream computing (Schmid 2004). However, there are certain factors that limit efficiency of systems that rely on this approach. Achieving satisfying levels of instruction-level parallelism depends on efficiency of branch prediction performed by hardware or software. It is not trivial, which was proved as early as in 1991 (Wall 1991). Additionally, cache miss penalty to main memory which costs hundreds of CPU cycles and complexity of hardware that needs to be built often reduce benefits that can be achieved from implementing instruction-level parallelism (McKee 2004).

<sup>&</sup>lt;sup>1</sup> Information is used in the context of "data" in this document, unless stated otherwise.

More recent advancements in development of hardware for performing computations have mostly been emphasising importance on increasing the number of cores that reside on the chip, rather than experimenting with changing the clock rate or improving methods behind instruction-level parallelism. As a result a new type of systems powered by a single processor that incorporates more that one central processing unit (or "cores") was developed (Rouse 2007). These cores are responsible for reading and executing instructions given to the CPU by programs. Adding additional cores onto the silicon base to improve performance increases the upper bound of amount of work that can be done by the processor by a factor of the total number of cores that the CPU obtains (Gove 2011). The motivation behind switching to multi-core systems resides in the fact that improving serial performance (performance of CPUs with one core) has become increasingly hard.

#### 3.1.1 Memory Cache in Multi-core Systems

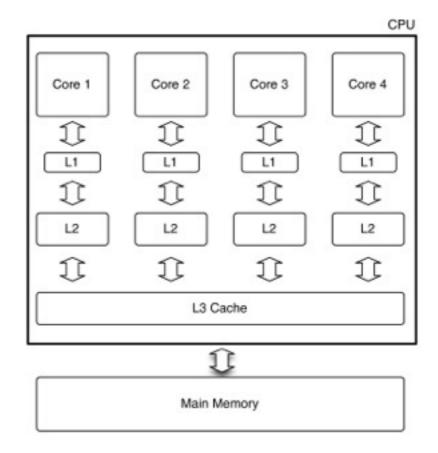

Multi-core systems also came with new memory cache approaches. As an example, IBM, does not use separate caches in its multicore server chips at all. On the other hand, Figure 3.1 outlines a more typical cache hierarchy model, used in, for example, Intel's Itanium and AMD's Opteron chips for servers and workstations, where each CPU core has its own private Level 1 (L1) and Level 2 (L2) data and instruction caches. The Level 3 (L3) unified cache is normally shared between all cores. Also, all core's L1 and L2 caches reside on the same die as the core and cannot be accessed by other cores. The cores are each connected to the L3 cache via the shared data bus. Allowing any processor to access any processors' cache memory is problematic, since there are no direct physical connections between different caches. If one core requires access to data that resides in another core's cache, the only path through which it can be achieved is the system bus. Assigning separate cache to each core removes the extra work required to design chips so that multiple cores can work with a single, centralized cache. (Geer 2005)

Figure 3.1 Three components connected by two channels.

As mentioned in Chapter 2 above, this project aims to investigate efficient memory management and thread placement schemes for Insense on multi-core systems. Insense is discussed in the following Section.

# 3.2 Overview of Insense Language

Insense is a high-level programming language developed at the University of St Andrews (Dearle et al. 2008). The initial goal behind creating the language was to decrease the complexity of developing Wireless Sensor Network (WSN) applications by abstracting over such concepts of programming as synchronisation, memory management and event-driven programming. The language was built to be run on two operating systems: Contiki (Lewis, Dearle 2011) and InceOS (Harvey et al. 2012).

This language relies on the idea of having components as basic computational units - building blocks - of applications. They serve as units of concurrent computation (Sharma et al. 2009). In Insense, the complexity is supposed to be borne by the language implementation rather

than by the developer. Components may be composed in a fractal manor because components can create instances of other components (Dearle et al. 2008).

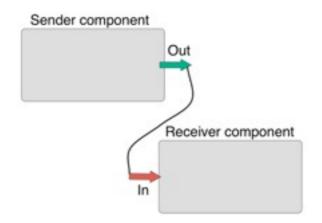

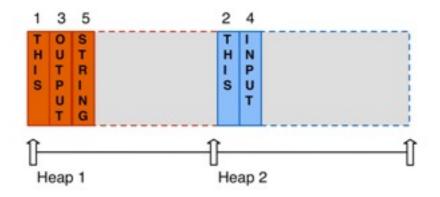

Moreover, Insense components are strongly encapsulated: they are stateful and the only medium of inter-component communication is usage of channels. To avoid unintended sharing of variables, an Insense component cannot reference any external data objects or locations. All inter-component communication passes through channels. Further, channels are typed and directional. All elements of the language including components and other channels can be shared through channels. Communication through them is synchronous: operations involving sending data are blocked until the messages are received and receive calls are blocked when there is nothing to be received. Figure 3.2 below shows two components Sender and Receiver that are connected by two channels; the Sender component sends data, the Receiver component receives it.

Figure 3.2 Topology with two components connected by a single channel.

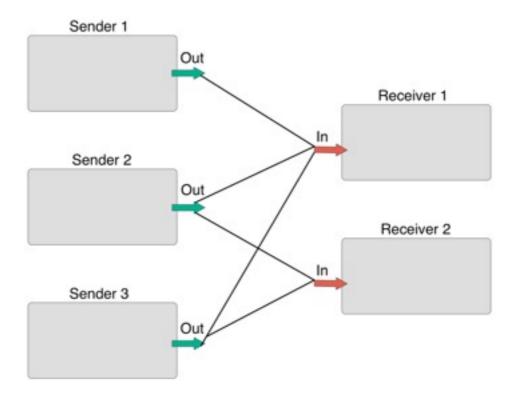

More complex topologies can also be described by Insense components and channels. Figure 3.3 below features five components interconnected by five channels. The components presented in the diagram can be divided into two categories: *senders* who send data on channels and *receivers* that receive data from channels. In this case datum is sent by Sender 1, by Sender 2 or by Sender 3 will be received by either Receiver 1 or Receiver 2, but not by both. If only one of the receivers is ready to receive, then the receiver that is ready will receive the datum, otherwise it could be either receiver which receives the datum. This latter case demonstrates that send and receive have an element of non-determinism.

Figure 3.3 Topology with five components connected by nine channels.

Insense was designed for sensory systems that are often used by people that have no background in computer science. It was created to be an easy to use programming language with syntax that is not difficult to learn and use to most (even unskilled) programmers. Handling of memory management that is often problematic in languages like C is not required from developers that use Insense.

#### 3.2.1 Components and Channels in Insense

All basic building blocks of Insense - components - are assigned with a type. The type of the component is described by its interface, which can contain any number of channels via which it may interact with other components. Figure 3.4 illustrates a "Hello World" example program written in Insense. It features one component that prints "Hello World" in its behaviour function. All Insense components are active and their activity defined by a syntactic construct identified by the keyword behaviour. The behaviour block may be likened to a single-threaded function which loops until explicitly stopped by using the stop keyword.

```

1.

type IHello is interface () // Interface for Hello component

2.

component Hello presents IHello { // Hello World component

3.

count = 1

4.

constructor() {

5.

}

6.

behaviour {

printString("\nHello World ")

7.

printInt(count)

8.

9.

count := count + 1

10.

}

11. }

12.

13. hello = new Hello() // Create and test component

```

Figure 3.4. "Hello World" program written with Insense language. (Lewis 2013)

Insense components are instantiated by using constructors that are defined in a similar manner to Java, C++ or C#. An Insense component declaration must contain at least one constructor. These constructors permit component variables to be initialised. A keyword presents follows a definition of a component, it is followed by a number of interfaces that the component presents for interaction with other components.

The Hello component in Figure 3.4 presents the IHello interface which in this simple example program does not contain any channels. It has a local variable called count. Declaration is done using the "=" symbol. Variables declared inside of components are local and they cannot be accessed from outside of their declaring component. The scope of variables declared inside of components is until the end of the scope of the component. The value of count is updated by using the ":=" assignment operator in the behaviour function.

As mentioned before, Insense components are strongly encapsulated. Channels have a role of being the only medium for inter-component communication.

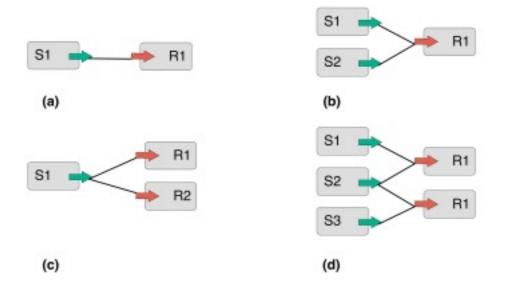

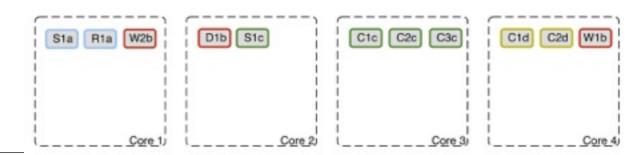

Figure 3.5 Connection topologies supported by channels in Insense. (Sharma et al. 2009)

Figure 3.5 (a) represents a one-to-one connection between a sender component 51 and a receiver component R1. The semantics of sending and receiving data over a one-to-one connection are similar to sending data with use of a traditional pipe: all values sent by 51 are received by R1 in the order they were sent. (Sharma et al. 2009)

The connection topology shown in Figure 3.5 (b) outlines a many-to-one connection pattern in which a number of output channels from one or numerous components may be connected to an input channel associated with another component. For this topology, R1 nondeterministically receives values from either of sending components on a single incoming channel. The receiving component cannot determine the identity of the sending component or the output channel that was used to send the message. Also, the arrival order of messages is determined by scheduling algorithm in use. The pattern is useful as a multiplexer in which R1 can multiplex data sent from 51 and 52 and could forward the data to a fourth component. The multiplexer pattern is utilised to allow multiple components to connect to a single shared output channel.

The topology in Figure 3.5 (c) shows a one-to-many connection pattern between a sender component S1 and two receiver components R1 and R2. Each value sent by S1 is non-deterministically received by either R1 or R2. Values are received only by one of the connected to the source of data components. Also, for the sender it is irrelevant which component receives sent data. An example scenario for the one-to-many connection pattern used in

Insense is that a sender wishes to request a service from an arbitrary component in a server farm. Each of the three basic patterns of connectivity depicted in Figure 3.5 (a) - (c) may be modified and extended to create further variations. Figure 3.5 (d) shows an example variation combining the patterns from Figure 3.5 (b) and Figure 3.5 (c). (Sharma et al. 2009)

```

type ITempReader is interface ( out bool tRequestChan ; in integer

1.

tValueChan)

2. component TempReader presents ITempReader { // Temperature reader

3.

constructor() {

4.

}

5.

behaviour {

6.

send true on tRequestChan

7.

receive temp from tValueChan

printString("\nTemp = ")

8.

9.

printInt(temp)

10.

}

11. }

12.

13. tr = new TempReader()

14. connect tr.tRequestChan to sensors.tempRequest

15. connect tr.tValueChan to sensors.tempOut

```

Figure 3.6 Insense application with a temperature sensor and two channels. (Lewis 2013)

The example illustrated in Figure 3.6 has two channels associated with the component. Interfaces that the component presents are listed on the type declaration stage: out bool tRequestChan ; in integer tValueChan. Interfaces describe how instances of components can interact with each other. In this example, the TempReader component has channels named tRequestChan and tValueChan. Keywords in and out specify direction of the channel: channels can be used for sending data (out) and receiving it (in). Also, a type of data that channel is meant to receive needs to be declared, in the example above the tRequestChan channel permits data of type Boolean to be sent and the tValueChan receives integers.

# 3.2.2 Data Types

Insense supports most data types that can be found in other programming languages, including: integer, real, Boolean, byte and enum. In addition, it supports structs, enumerations, and arrays similar to those found in many other programming languages such as Java or C++. (Dearle 2011)

```

1. newArray = new integer[3][3][2] of 0

```

In Insense, arrays must be given a predefined size and they have to be initialised on declaration. Figure 3.7 shows an example of array declaration: in this case a multidimensional array (array of arrays of arrays) of integers was created, all elements inside of it are initialised to 0.

```

1. type Car is struct( string model; integer miles )

```

2. car1 = new Car( "mlsb", 4000 )

Figure 3.8 Creation of a structure and an instance of it.

Figure 3.8 shows that structures may be defined by using the keyword struct. In order to permit static worst-case size estimation of components and their data, Insense structs cannot contain references to other structs. Therefore, structs can be formed from all other data types, other than other structs. Structures are instantiated by using the keyword new.

In Insense functions can be declared either as global (outside of components) or as component local declarations.

```

1. proc multiply(integer i, j,) : integer {

2. return i * j

3. }

```

Figure 3.9 Function declaration in Insense.

Figure 3.9 presents an example of a global function that performs multiplication of two integers that is visible to all components in a compilation unit. On the other hand, locally defined functions can be accessed only by the component that contains the definition.

# 3.3 Memory Management in C Language

In C, there are two ways of allocating memory for variables:

- Static allocation is used when one declares static variables. One block of space is allocated for each static variable, its size cannot be changed and it cannot be freed manually. The allocated piece of memory is freed when the application that used it stops.

- 2. *Automatic allocation* is called when developers create automatic variables (e.g. local variables or function arguments). Space for variables of this type is allocated when a

compound statement that contains the variable is entered; it is freed when the statement is exited.

In C, variables are not dynamically allocated on the heap. However, blocks of memory can be dynamically allocated on a heap and their base addresses are then stored in variables of an appropriate pointer type. This process is known to require more computational time and programmers tend to use it when static and automatic allocation cannot be utilised. The most common method used for dynamic memory allocation is utilisation of a single shared (big) heap structure, where a program can ask for a block of memory to store an object, and request that block to be deallocated at any time during execution of the computer program. A heap is a pool of memory available for the allocation and deallocation of arbitrary-sized blocks of memory (Wilson et al. 1995). Most of the basic design used for implementing memory management with shared heaps was achieved in the 1960's (Knuth 1997).

Data is allocated into contiguous and nonoverlaping ranges of memory. Generally, only entire blocks are allocated or freed, and the allocator is unaware of the type of or values of data stored in a block, it only knows the size requested.

#### 3.4 Utilising Private Heaps for Memory Management

To refine the effective memory hierarchy performance in multithreaded applications, a number of hardware solutions have been proposed. Methods such as tiling and thread scheduling used for cache locality are a few examples of known techniques (Park, Hong & Prasanna 2003, Philbin et al. 1996). This project focuses on moving away from the idea of using one large heap for memory management and going towards utilisation of private heaps instead. It is seen as a way to improve performance and efficiency of memory management in multithreaded applications.

There is no functionality in the C standard library that permits programmers to make use of separate private heaps for individual threads or processes. However, this project seeks to design and implement a version of Insense that permits memory to be allocated on private heaps as opposed to the standard single shared heap offered by the standard library. The motivation for this work is that memory management can be more efficient when multiple

private heaps are used. There are a number of reasons why this is a case ("*Managing memory*"<sup>2</sup> 2013):

- 1. Allocation into a single heap often creates memory blocks that reside in different pages of memory. As an example, let us consider allocation of memory for items of a linked list. If one allocates memory for other data between adding nodes of the list, the blocks linked with nodes of the list may end up on multiple different pages. It means that accessing data from the linked list would potentially involve swapping multiple pages, jumping from one page to another. Utilisation of multiple private heaps implies that one can specify which data is allocated in which heap. It allows reduction of overhead created by swapping between pages of memory since data that is often accessed at the same time (in case of the example before: data stored in the elements of the linked list) can be stored in fewer pages, and it remains close together.

- 2. Applications dealing with multiple threads can benefit from using private heaps as well. The reasoning goes as follows. Using a single large shared heap as a memory resource, no more than one thread can allocate memory into a heap at the same time. The reason for this restriction is to ensure that memory is safely allocated and deallocated in the shared resource. As such, allocation and deallocation of memory in a single heap shared by multiple threads must be serialised via mutexes or semaphores. This slows down allocation and deallocation due to threads having to wait until they can access the shared resource. Performance could be improved if a separate private heap is created for each thread, reducing both the time that threads have to wait and the overhead needed for serializing access to the heap.

- 3. Private heaps could also be created for specific data structures (we may take the example dealing with the linked list from point 1 of this list into account). If one has a linked list that has its elements allocated in various pages in memory, freeing the blocks must be done individually, which can take time. If a separate heap is created specifically for that list, deallocating the whole list could be done by a single call that destroys the entire data structure. In this case, freeing memory could be made more efficient and performance could be improved. This scenario is not investigated in this project.

- 4. Another drawback of using a single shared heap for memory management becomes apparent when a large number of allocations and deallocations of data of the same large

<sup>&</sup>lt;sup>2</sup> Citations of references with no author are given by the first few words of the title and year.

size take place. With time, memory space may not be able to fit in any more large data due to adding smaller pieces of information into memory between allocation and deallocation of large data. For example, if one has a block of free memory of size 1MB, allocating even 1B into that region makes it impossible to allocate another 1MB into the same block.

#### 3.5 Thread Affinity

Another aspect of multithreaded applications, placement of threads, may be shown to affect performance. Thread affinity allows to bind and un-bind threads to a physical CPU or to a range of CPU cores, rather than allowing threads to run on any core. In this way a thread will run only on a core or cores in question.

Mechanisms that allow thread affinity scheduling prove to be of growing interest since in modern machines amount of time needed to access a memory location cached locally versus one held in main memory is usually significantly lower. (Salehi, Kurose & Towsley 1995, Devarakonda, Mukherjee 1992, Gupta, Tucker & Urushibara 1991). Achieving successful and efficient affinity of threads may take advantage of speedup that can be received through accessing locally cached memory. By using thread affinity and avoiding dynamic placement of them programmers wish to reach such situations where work can be transferred for execution onto separate processors, when feasible and profitable.

Static affinity of threads can be beneficial for optimizing cache usage: a number of times the program must switch processors can be significantly reduced, which lowers a rate of flushing one cache and repopulating another. Additionally, thread affinity takes advantage of the fact that cache used by the thread may store data that was put there during one of the previous runs (Yang 2010). Research in the field of static thread affinity has been ongoing for more than 20 years now (Vaswani, Zahorjan 1991). We intend to investigate to what extent performance of programs and utilisation of cache may be improved by statically setting the processor affinity of threads in Insense.

#### **4 SOFTWARE ENGINEERING PROCESS**

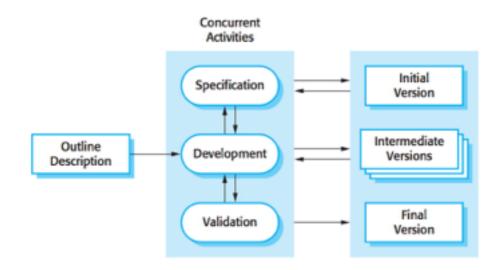

This Section touches issues connected with principles of software engineering that were employed throughout the work on the project. Multi-core Insense was developed by following concepts of evolutionary (incremental) development. Figure 4.1 outlines main stages that projects which follow the model go through. Incremental software development is known to be better than a waterfall approach for most business, e-commerce, and personal systems (Sommerville 2011). The evolutionary development model was chosen due to its characteristics that seemed to be promising for a project of this type and scale. Firstly, this method is beneficial for a project that in its objective has creation of a part of a large system (*"Understanding"* 2006). Such risks as missing deadlines, creating unusable products of low quality can be addressed and managed by breaking the project into smaller, more manageable pieces (May, Zimmer 1996).

Figure 4.1 The evolutionary development model. (Sommerville 2011)

At first, a *description* of the project was outlined. Research goals, system's objectives and constraints were established on this stage. The main goal was defined as successfully analising benefits of using schemes of memory management and thread placement discussed in the scope of this project. Outline requirements were specified for Multi-core Insense prior to starting the evolutionary development cycle.

#### 4.1 Project Plan

After outlining description of the project, it entered the *implementation* phase where the more detailed design and implementation of the system took place. Work was conducted in cycles. As can be seen from the Figure 4.1 above, each cycle consists of three main concurrent activities: gathering *specifications*, conducting *development*, and *validating* results. Three main stages can be outlined: 1. Insense was ported to Unix. 2. A number of methods utilised for management of memory were first designed and then implemented. 3. Schemes of

placement of threads were designed and implemented. The initial, intermediate, and final versions were created. Multiple intermediate versions were achieved by following feedback received through validation of cycles of design/implementation.

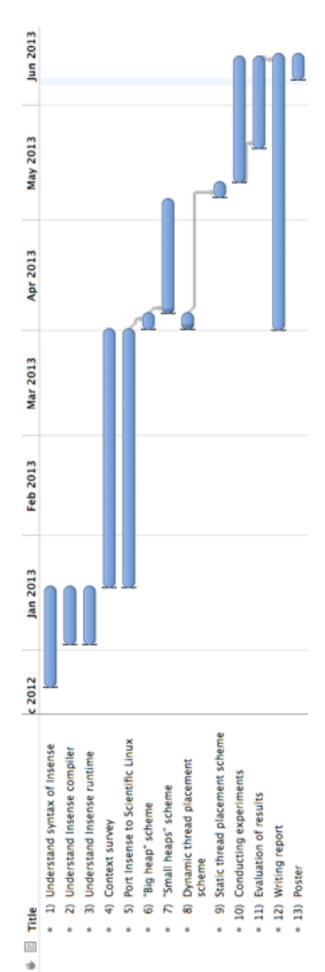

The time scale of the project was around five month. More than a half of this time was spent on understanding Insense and software systems behind it and working on the base implementation that allowed designing, implementing and eventually experimenting with memory management and thread placement. Appendix 2 contains a Gantt chart for the project that was used to orgranise work.

# **5 REQUIREMENTS SPECIFICATION**

A number of outline requirements were established on the initial stage of the project.

# **5.1 Functional Requirements**

Functional requirements describe how the system should and should not behave, what kind of services it should provide and what type of output it should produce when it is given certain kinds of input (Sommerville 2011). The following list of initial (outline) requirements was established for the project:

# Components:

- 1. The system must be able to create, assign to POSIX threads, and stop components.

- 2. When on multiple cores, components must be able to run in parallel.

- 3. Components must be able to communicate with other components through channels.

# Channels:

- 4. The system must be able to create, destroy, bind together and unbind channels.

- 5. Channels must be able to serve as a medium for transferring data of such types as integers, strings, arrays etc.

- 6. Channels must support 1:1 and N:M connection types (described in Section 7.3).

# Memory management:

Support for allocation and deallocation of memory into a single shared heap and into multiple private heaps must be given.

# Thread placement:

8. Support for the following schemes of thread placement: 1) dynamic placement, where OS takes care of setting affinity; 2) static placement, Insense components are distributed evenly among cores; 3) all components are placed on a single core; 4) locating Insense components based on frequency of communicating with other components

Insense Compiler and Runtime:

- 9. Insense programs must be able to run on a 64-bit architecture.

- 10. Users must be able to choose among supported data placement scheme.

- 11. Users must be able to choose among supported thread placement scheme.

# **5.2 Non-functional Requirements**

Non-functional constraints are normally put on the services or functions offered by the system. To name a few, this type of requirements includes constraints on the development process, timing constraints, and constraints imposed by standards. (Sommerville 2011)

The following non-functional requirements were outlined for this project:

- 1. Keep changes to the Insense compiler to a minimum so as to maximise compatibility with existing versions.

- 2. The project must be finished and results delivered by June 26<sup>th</sup> 2013.

- 3. Updates on achieved progress must be given to a supervisor on weekly basics.

# **6 ETHICS**

This project did not involve conducting experiments that require participation of humans. As such, there were no ethical concerns associated with this project. Appendix 10 contains a scanned copy of the ethics approval form.

# 7 DESIGN

This Section summaries design process that was undertaken in the project and discusses taken design decisions.

#### 7.1 Design of Multi-core Insense

In order to successfully use Insense on a multi-core Unix-based system a number of essential elements of the language had to be redesigned.

#### 7.1.1 Components

A component is active and the unit of concurrency in Insense. For the Contiki-based implementation, component behaviour was represented using proto-threads, a light-weight form of thread provided by the Contiki OS. Under InceOS, behaviour of components was embodied by utilising an active and pre-emptable component abstraction provided by InceOS. For the Unix implementation, component behaviour could either be represented using Unix Processes or POSIX threads (p-threads).

A decision was taken to use POSIX threads because threads are commonly considered to be more light-weight than processes in consuming less resources in the OS (Stallings 2009). Further, component communication over channels is likely to be easier to design and implement when components are represented as threads as these may communicate via a shared virtual memory space without the need for additional Inter-Process Communication (IPC) mechanisms when communicating between different processes.

The following operations on components must be supported by the multi-core Insense runtime:

- Creation of components: a POSIX-type thread is created and the component behaviour will be implemented by the new thread. If private heaps are utilised for memory management, as discussed in Section 7.2.2 below, a new heap assigned to the component is created at this stage. Also, if required, thread affinity can be set, as discussed in Section 7.3.

- 2. *Stopping components*: the thread implementing the component's behaviour is stopped. It is achieved by changing value of a Boolean flag that indicates whether component is running or not to FALSE, as discussed in more details in Section 8.1.1.

#### 7.1.2 Channels

A decision was taken to use the algorithms proposed in (Sharma et al. 2009) for this project. The reason behind using these algorithms is that they have been verified by the scientific community and successful experimental results were achieved, as described in the aforementioned paper.

receive( half\_channel cin ) { wait ( cin.conns ) // wait for conns wait ( cin.nutex ) // lock rovr set( cin.ready ) // signal rovr ready signal ( cis.mutex ) // release rcvr foreach( halfchan match in cin.connections ) wait ( cis.mutex ) // lock revr wait ( match.mutex ) // lock sndr if ( match.ready && cin.ready) {// both ready cin.buffer = match.buffer // copy unset( match.ready ) // both no longer unset( cin.ready ) // ready signal; match.blocked ) // let sndr run signal match.mutex ) // release sndr signal; cin.mutex ) // release rovr signal (cin.conns ) // incr conns return signal ( match.mutex ) // release sndr signal ( cin.mutex) // release rcvr signal ( cin.conns ) // incr conns wait ( cin.blocked ) // block revr return

Figure 7.1 Send and Receive algorithm proposed by (Sharma et al. 2009).

Figure 7.1 above outlines algorithms for send and receive operations. The design of these functions is almost symmetric, as can be seen in the algorithms. Both operations check whether any components are waiting in the list of connections with the sender looking for a waiting receiver and vice-versa. If no such match is found the sender or receiver blocks on the blocked semaphore until it is re-awakened by at least one component moving to the state that allows sending/accepting data.

In addition to the send and receive operations in Figure 7.1 above, a number of other operations are required to support channel communication in Insense. These include creation of a new channel with given payload type and direction and connection and disconnection of component channels. The channel operations are described in more detail in (Sharma et al. 2009).

# 7.1.3 Program Entry Point

Under Unix, it was necessary to design and implement a system-level entry point to the entire Insense program. This entry point may be likened to the main function in a C program or the main method in Java. It was decided that such a main function should be defined once in the Insense Runtime library and should be designed to instantiate any necessary data structures and then hand over control to a programmer-defined entry point in the Insense program.

Insense programs commonly contain declarations of any global procedures (for use by all components) followed by component declarations and finally a sequence of code that serves as the user-level entry point to the program, i.e. where user-level program execution begins. In InceOS, this entry point was represented as a schedulable InceOS component and in Contiki, it was represented as a Contiki process. Under Unix, a decision was taken to represent the programmer-defined entry point as a function that is called by the system-level entry point as explained above.

Any dynamically allocated memory required by the main thread is handled by using the malloc function. Hence, even when the "private heaps" scheme is in use, memory required by the main component will be allocated dynamically, into the shared heap. The main thread requests allocation of memory for a little amount of data: one descriptive string per component and for what is passed as members of the argv array of program arguments. This design decision was made since it may be argued that the amount of dynamically allocated data required by the main thread is minimal and location of it does not affect experiments involving private heaps that are outlined further in this document.

# 7.1.4 Memory Management & Garbage Collection

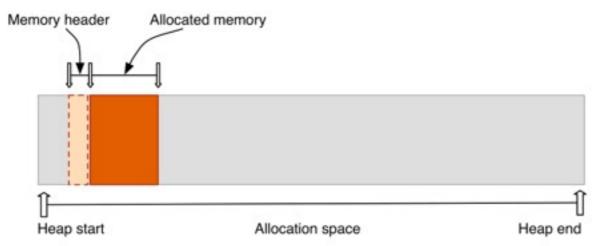

Insense uses a special reference-counting garbage collection scheme for dynamically allocated memory. With this method, each allocated block of memory is prepended with a piece of memory that stores information about the allocated memory range.

Figure 7.2 Header prepended to allocated memory (in the shared heap).

The number of references to every object dynamically allocated in Insense is accounted for and stored in the memory header. Whenever Insense variables are assigned to dynamically allocated data (such as an array, channel, component, struct, any) the reference count in the memory header is adjusted to reflect the assignment. Whenever a reference count reaches zero, when it is no longer referenced by any variable, the object is considered as ready to be "garbage collected"/destroyed. Moreover, the process of garbage collecting recurses down and it deallocates memory assigned for all objects that depend of the object that needs to be garbage collected (e.g. elements of an array). Figure 7.2 shows a schematic diagram that outlines how a header is attached to a dynamically allocated region of memory.

# 7.2 Data Placement Schemes

Two data placement schemes were designed. The final design of the system permits memory for dynamically allocated objects to be allocated in one shared large heap and in multiple small private heaps.

#### 7.2.1 Shared Heap

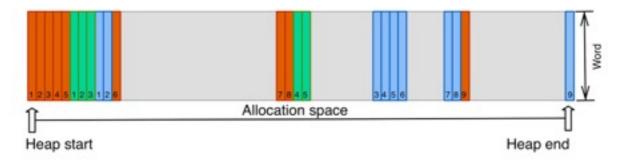

In this scheme, memory is allocated dynamically for Insense components, structures, arrays or channels at runtime in a single shared heap.

Figure 7.3 Dynamically allocated memory for three components inside of the shared heap.

Data allocated by different threads inside of one Insense program is not separated. Figure 7.3 demonstrates a possible scenario where three Insense components make use of a shared heap, colours represent memory allocated by different components. Allocated memory is numbered, based on order of allocations taking place in each thread. Areas of grey colour between allocated memory indicate free fragments of the allocation space. The design of the "shared heap" allocation mechanism merely requires adoption of the standard library mechanisms available in C, as these allocate on a single shared heap.

As indicated in Figure 7.3 above, memory allocated by particular threads may become fragmented and dispersed over the shared heap depending on the interleaving of allocations and deallocations by different threads. Also, as already mentioned in Section 3.4 above, allocation into the shared heap by multiple threads will be serialised. The issues surrounding fragmentation and concurrent access to a single shared heap from multiple threads are discussed in more detail in Section 3.4 above.

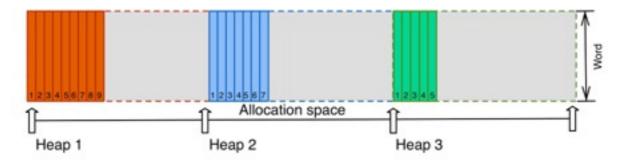

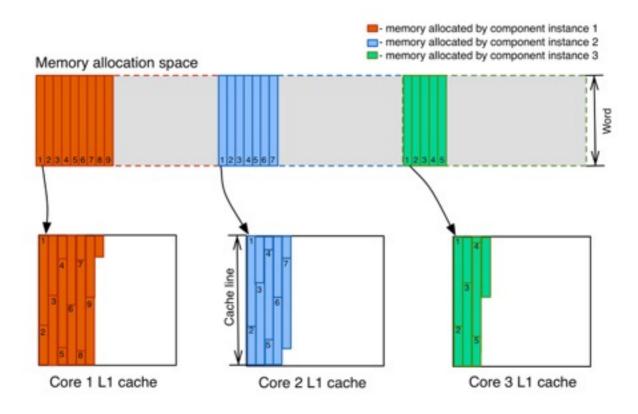

#### 7.2.2 Private Heaps

For Insense on multi-core Unix, it was decided to investigate a different memory management mechanism to that discussed in Section 7.2.1 above, where each component is given a small private heap in which dynamic allocation of memory can take place. Figure 7.4 shows a diagram with three components that allocate memory into private heaps that were assigned to them (represented by different colours). The allocation space now comprises three heaps. This illustration contrasts with a Figure 7.3 in the previous section where allocation is performed into a single shared heap. Similar to the previous figure, numbers indicate ordering of allocation within each thread. Although the exact sequence of the various components' allocations may take place in any order in time, allocated memory is inputted into one private heap and it is contiguous in space.

Figure 7.4 Dynamically allocated memory for three components inside of private heaps.

The most significant advantage of this scheme is that multiple threads can allocate in their private heaps concurrently, whereas threads that allocate into one large heap have serialised access (with mutex locks). Another advantage of this scheme is that when memory required by one thread is allocated contiguously into the same heap, the likelihood of allocated data residing in one page of allocation space is higher, compared to the "shared heap" scheme. Hence, performance of the program may be improved by reducing overhead created by swapping multiple pages.

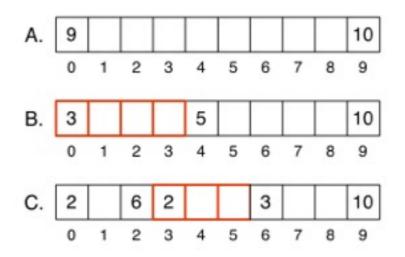

# 7.2.3 Data Placement and Potential Cache Misses

Another problem that systems which work with dynamic allocation of memory face is cache misses. When a program accesses a data item for the first time, the data item will be hauled into a fast cache close to the processor (prior to access) from the next-level cache or main memory, which costs time. Cache misses occur whenever a program tries to access an uncached data item (Gove 2011, Hennessy 2007). A data item may be uncached because it has *a*) never been accessed before (compulsory miss) or *b*) it has been accessed before, but had to be evicted from the cache when another data item was accessed by the program (conflict miss). Cache misses impact on performance because they may result in the processor having to wait (stall) while the data item is cached. Much research has been done in the area of reduction of the number of cache misses that occur during execution of a program, there is a number of parameters that can be tweaked for receiving gains in performance: size of cache, associativity, block size etc. (Wulf, McKee 1995, Ghosh, Martonosi & Malik 1997, Lam, Rothberg & Wolf 1991)

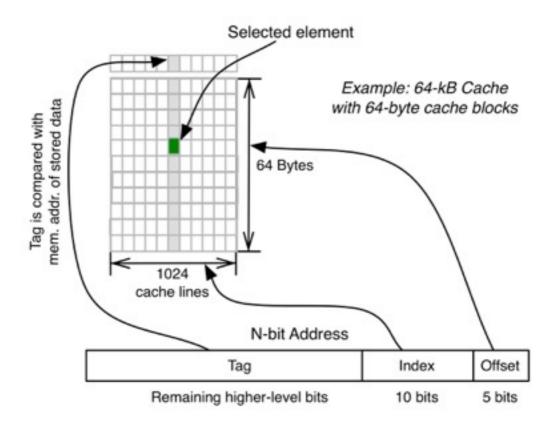

The level 1 caches used in most computers today are either directly mapped caches or set associative caches (Handy, 1998). In case of a directly-mapped cache, each location in main

memory can only be put into one cache line in the cache. When the cache is set associative, instead of mapping every address to a particular cache line, every address maps to a particular set of a certain number of cache lines (e.g. 8), but can be placed in any of the cache lines within that set.

Figure 7.5 shows how the *Offset* and *Index* portions of the memory address specify where the datum may be placed and retrieved in a directly mapped cache. The *Index* portion of the address specifies the cache line and the *Offset* where the datum is within that cache line. A *Tag* that represents a significant part of the memory address is also stored with each cache line and is used to record the remaining higher parts of the memory address of a datum that is held in the cache. When a system attempts to access a data item from memory, the *Tag* stored in the cache line is compared to the *Tag* portion of the address that is being accessed in order to determine if the requested data item is cached or not. In case of a set-associative caches, the *Index* indicates which set of cache lines can be utilised to cache a datum with a given memory address. Within that set, any unused cache line among the cache lines in the set can be used, or one must be evicted prior to caching the new datum if they were previously all in use. As before, the *Tag* is used to store the higher-order bits of the memory address to indicate which address is actually cached in the cache and the *Offset* locates a datum within a specific cache line.

Figure 7.5 Retrieving data from directly mapped cache.

When a core has access to more data allocated in the main memory than can fit inside of the L1 cache, which is often a case, certain blocks of memory are linked to the same location inside of the cache. The main idea of set-associative caches is to reduce the chances of conflict misses because for any memory address there is a number of possible cache lines to use rather than a single line in the direct-mapped cache. However, both the directly mapped and the set associative caches suffer from high rates of cache misses (Hill 1988).

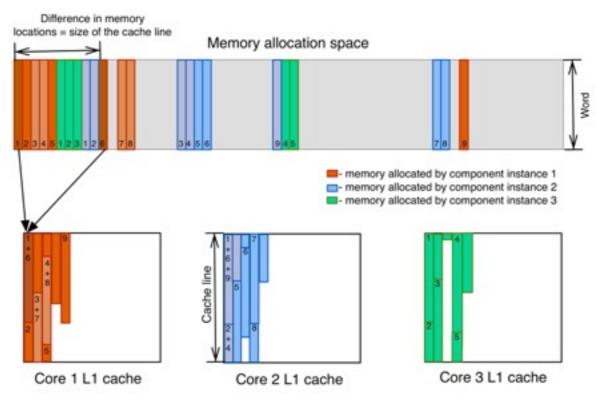

Figure 7.6 Cache misses with the "shared heap" scheme.

The "shared heap" scheme utilised for memory management in multi-core Insense is expected to be affected by conflict misses due to memory fragmentation to a greater extent than the "private heaps" scheme where fragmentation is anticipated to be less common. An example of the issue of cache misses can be understood when Figure 7.6 is taken in account. This diagram illustrates occurrence of cache misses in a system that uses a single shared heap for memory and has a directly-mapped cache in its processor. Multiple components are executed on different cores. Level 1 caches of three cores are represented on the illustration. The size of each cache line is a number of words, the exact number of words can be left undefined for this discussion. Data allocated by three component instances is fetched from main memory and placed into cache. Here we assume that a difference between memory addresses of blocks 1 and 6 of instance 1 (red) equals to the size of the L1 cache. These blocks are represented with different shades of red in the diagram. Based on the description of the mechanisms behind the directly mapped cache, one notices that block 1 and block 6 both map to the same cache line. As a result, when a system wishes to retrieve data stored in the red block 1, a cache miss will occur if block 6 was accessed previously. Similar logic can be applied to other blocks of memory where cache misses will eventually occur. Additionally, Red blocks 3 and 7, 4 and 8; Blue blocks 1, 3 and 9, 2 and 4 will create similar cache misses. They are also marked with

different shades of their representing colour in the figure. A similar situation occurs when a set-associative cache is used. Only a number of cache misses is lower due to the fact that allocated memory maps to a particular set of cache lines. Hence, chances of a particular cache line being overwritten by data from main memory are reduced by a factor of the size of the set.

Figure 7.7 Cache access with the "private heaps" scheme.

Figure 7.7 attempts to show that a number of cache misses can be reduced if private heaps are utilised for memory management. Similar to the example involving Figure 7.6 described above, cache misses are possible when private heaps are used. However, because memory allocated inside of private heaps is contiguous, a number of cache misses is significantly lower, compared to the "shared heap" scheme. As a result, we would expect to see a performance increase and reduced number of cache misses for the "private heap" scheme compared to the "shared heap" scheme.

#### 7.3 Thread Placement Schemes

Another aspect that may affect performance of applications written in Insense and running on multi-core systems is placement of threads that are responsible for behaviour of Insense components.

#### 7.3.1 Dynamic Placement

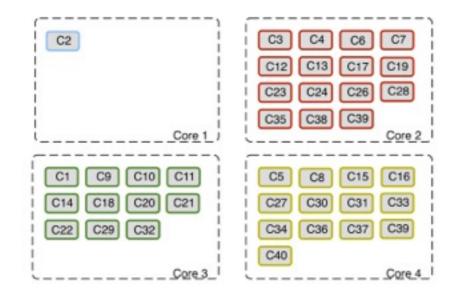

The first scheme of choosing affinity that was considered in the scope of this project is dynamic placement of threads implementing Insense component behaviour. With this method, affinity of threads is handled by the operating system.

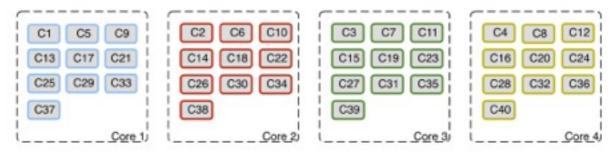

Figure 7.8 40 threads linked to Insense components dynamically placed on 4 cores.

Figure 7.8 illustrates how thread placement is handled on Unix-based machines. In this example the OS decided to place a single compute-intensive component instance C2 on Core 1 in order to balance the execution load of the cores. Thread affinity is handled by live migration of threads to different cores. Unix-based systems use the hybrid (push/pull) migration algorithm for multiple-processor scheduling: *push* - the systems have a special task that checks the load on each processor every 200 ms; *pull* - a free processor takes a task from another processor that has higher load (Garg 2009). As a result, a computer program has no knowledge of which threads are placed on which cores. We intend to investigate the impact on performance, since efficiency of cache utilisation may suffer.

# 7.3.2 Static Placement

The alternative approach to dynamic placement of threads is setting affinity statically. The program or the programmer or, possibly, the compiler decides a core that a particular thread is pinned to. Threads can be associated with a particular core during the whole duration of the program's execution. Statically setting the affinity of threads can be beneficial for optimizing cache usage: a number of times the program must switch processors can be significantly

reduced. It lowers a rate of flushing one cache and repopulating another. Deciding on the core that is used for setting affinity to a thread is not straightforward and it may be done by involving various approached and algorithms. In the scope of this project three methods of setting static affinity to threads are investigated:

1. *Even distribution among cores*: an algorithm similar to round-robin scheduling algorithm (Silberschatz 2009) is experimented with. A pool of cores available for setting affinity of threads is traversed circularly. Figure 7.9 demonstrates an example. In this diagram 40 Insense component instances are distributed between 4 processors. If one assumed that amount of computation performed by all components is uniform, it would be possible to say that all cores in the CPU perform approximately the same amount of work.

Figure 7.9 40 threads linked to Insense components statically placed with the "Round-Robin" algorithm.

2. *Assignment of threads to a single core*: threads are linked with a particular core. Figure 7.10 outlines a system where all Insense components are assigned to one core (in this case Core 1). Investigation of utilisation of this scheme is a part of this project since in some circumstances it may be beneficial to performance of the program.

Figure 7.10 40 threads linked to Insense components statically placed on a single core.

This scheme is not expected to be particularly efficient other than for programs with intercomponent dependencies that restrict active computation to a single component instance at any particular point in time.

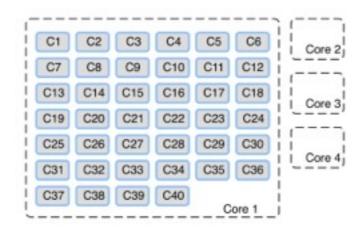

3. Assignment of threads to cores based on the nature of communication with other threads: threads implementing component behaviour are linked to cores based on the nature of communication with other Insense components that they undergo. To explain this placement scheme, an outline of three different patterns of component operation and communication between components is given next. Figure 7.11 below demonstrates five patterns:

(a) *Sender - Receiver (1:1)* : in this pattern one or multiple sender component(s) send data (e.g. an integer) and receiver component(s) receive data. No calculations take place on either side. This scheme outlines a case where a built system relies heavily on communication between components.

(b) *Dispatch - Worker (1:N)* : Consider a *Dispatch* component which always sends a number and *Worker* component which receives that number and then performs amount of work controlled by the number. The *Dispatch* will not be able to send another number until any connected *Worker* component instances have done their work and execute their receive statement again (because the channels are synchronous).

(c) *Client - Server (N:1)* : In this scenario, one or multiple *Client* instances send requests to a single *Server* which receives the request and performs computation of some kind. There is no need to reply to the *Client*.

(d) *Many to Many (N:M)*: this is a more complicated case which can be seen as a combination of patterns (b) and (c) above. Component instances on both sides of the diagram (components 1 - 3 and 4 - 6) can perform computation.

(e) *No communication*: in this simple case no communication between components takes place.

Figure 7.11 Component connectivity patterns.

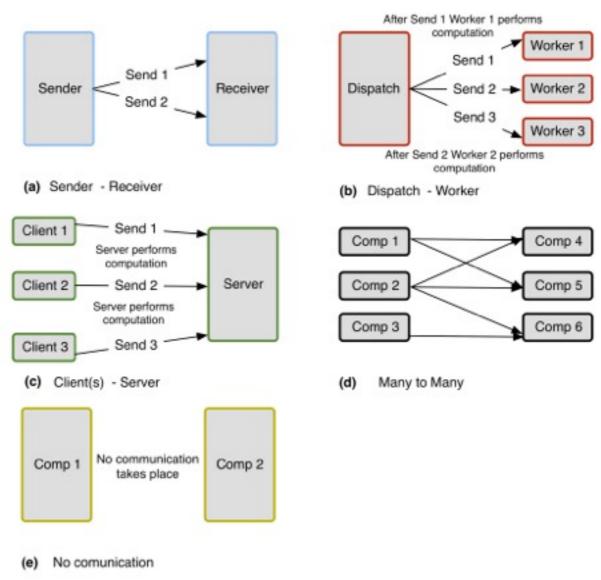

Figure 7.12 reveals an example with four different groups<sup>3</sup> of components: "a" (marked with blue borders), "b" (red borders), "c" (green borders), and "d" (yellow borders).

<sup>3</sup> The word "group" in this Section refers to Insense components in Figure 7.11 that are marked with the same ending letter and the same border colour. E.g. for the component "S1a", a letter "a" denotes the group of the component, which in this case is "a".

Figure 7.12 11 threads linked to Insense components statically placed on cores based on the nature of communication with other threads.

To continue with the example, let us assume that the following statements hold true:

- The group "a" of components may be described by the *Sender Receiver* example. R1a must wait to receive a value before it can do anything else and S1a must send a value before being able to do anything else. In this case executing both components on the same core may be beneficial: as neither can make progress while the other component is doing something other than sending or receiving.

- The group "b" of components may be described by the *Dispatch Worker* example. Component instance D1b is a *Dispatch* component and two instances - W1b and W2b - are instances of a *Worker* component. In this case executing D1b, W1b, and W2b on different cores may be beneficial in terms of maximising concurrency at the expense of more inter-core component communication.

- The group "c" of components may be described by the *Client Server* example. C1c, C2c, and C3c are multiple *Client* instances and S1c is a single *Server* which receives requests sent by clients and performs computation. We argue that with this scenario it may be beneficial to execute the clients (C1c, C2c, C3c) on one core and the server S1c on a different core.

- The group "d" consists of two components C1d and C2d that have no communication with any other components. This is an example of the "*No communication*" pattern.

This work aims to investigate the efficiency of dynamic component placement compared to static placement according to interaction pattern. Naturally, using only amount of communication with other threads as the only way parameter for deciding which cores a particular thread should be pinned to may not be efficient enough. One may think of multiple other characteristics: type of computations performed in the component, estimated execution time etc.

# **8 IMPLEMENTATION**

This chapter first describes how Insense was adjusted to run on Unix-based systems that operate with multiple cores. Then, a description of the main work performed on implementing schemes for memory management and thread placement is described.

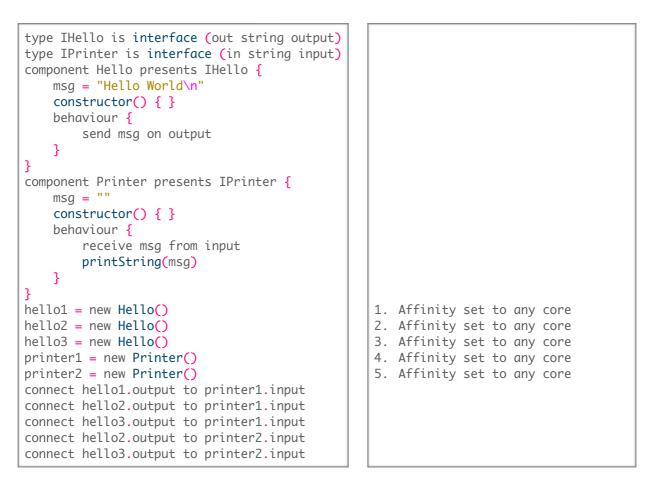

```

1.

type IHello is interface (out string output)

2.

type IPrinter is interface (in string input)

3.

4. component Hello presents IHello {

5.

msg = "Hello World\n"

constructor() { }

6.

7.

behaviour {

8.

send msg on output

}

9.

10. }

11.

12. component Printer presents IPrinter {

13.

constructor() { }

behaviour {

14.

receive msg from input

15.

16.

printString(msg)

17.

}

18. }

19.

20. hello = new Hello()

21. printer = new Printer()

22. connect hello.output to printer.input

```

Figure 8.1 The "Hello" program written in Insense.

Figure 8.1 presents the source code of a single example program written in Insense that will be used throughout the chapter. It will be used at various stages of explanation to showcase different aspects of the implementation of multi-core Insense. Essentially, it is a "Hello world" example. The program has two components: "Hello" and "Printer". The "Hello" component contains a string object, it sends the object over a channel to the "Printer" component, where the string is outputted on the screen.

#### 8.1 Base Unix Implementation

When the project was started, modifying Insense to an extent that allows running a demo application on a Unix-based system was set to be a minor step that needs to be taken in the beginning. While working on porting the language to Unix it was learnt that time commitment and amount of work had been largely underestimated. Every step that had to be taken to modify Insense came with issues that took time and effort that had not been previously expected. Working on this stage took more than two months. Problems that were met on this phase of the project could be explained by the fact that development was based around using two relatively large projects (Insense compiler and Insense runtime environment) that in total are comprised of more than 1,700 files written in three languages: C, Java and Insense itself. Additionally, the code is not well-documented. While working on providing support for executing Insense applications on multi-core Unix-based machines, a better level of understanding was achieved in how pieces of the whole system behind Insense fit together and what principles of software engineering were used in development of Insense language.

# 8.1.1 Components

Code related to Insense components may be found in component.c and component.h files.

The main difference between components in the form they are used in the multi-core implementation of Insense and variation of Insense designed for InceOS and Contiki resides in the fact that components are run on POSIX-type threads.

| 1. | <pre>struct IComponent_data {</pre>    |

|----|----------------------------------------|

| 2. | <pre>void (*decRef)(void *pntr);</pre> |

| 3. | <pre>bool stopped;</pre>               |

| 4. | pthread_t behav_thread;                |

| 5. | <pre>sem_t component_create_sem;</pre> |

| 6. | };                                     |

// The supertype for all components

// For ref counting garbage collection

// Has the component been stopped

// Process implementing behaviour

// Semaphore for component\_create

Figure 8.2 The supertype structure for Insense components.

Every Insense component instance is described by a structure that stores various metadata about a component in question. The original design of the structure used for this task that was developed for the InceOS and Contiki operating systems had to be changed to accommodate for the multithreaded environment. In the current implementation, each Insense component is described by the structure of type IComponent\_data, source code of which is given in Figure

8.2. The structure contains the following information about a component:

- void (\*decRef)(void \*pntr) pointer to a function used for reference counting garbage collecting described in Section 8.1.5.

- bool stopped Boolean flag indicating whether a component can run (set to FALSE) or if it has been stopped (set to TRUE).

- 3. pthread\_t behav\_thread This is a handle to a POSIX thread implementing the component instance's behaviour.

- sem\_t component\_create\_sem a semaphore used to avoid synchronisation issues that arise in the component creation stage where more than one component use private heaps for memory management.

To create a component, one needs to use the function void \*component\_create(behaviour\_ft behaviour, int struct\_size, int stack\_size, int argc, void \*argv[]). Appendix 4 contains source code of the function. The initial part of the function creates a structure \*this\_ptr of type IComponent\_data that is used for storing metadata described in the beginning of this section. Figure 8.3 shows that a mutex was added to the code of the component\_create() function, it is required to avoid problems with scheduling of threads.

- 1. pthread\_mutex\_lock(&thread\_lock);

- pthread\_create(&this\_ptr->behav\_thread, NULL, startRoutine, argStruct);

- pthread\_mutex\_unlock(&thread\_lock);

Figure 8.3 A part of component\_create() where component is assigned to a POSIX thread

Once the this\_ptr structure for the component is initialised, the component's behaviour function is ready to be run with the POSIX thread. This operation is achieved through calling the pthread\_create function ("*pthread\_create(3*)" 2013). This function allows passing only one parameter along with the function that is to be run inside of the thread. The component's this structure, the pointer to the Insense constructor function and its arguments are placed into a struct and passed to the start\_routine function as a single argument (as required by pthread\_create). The start\_routine is then able to call the Insense constructor. A wrapper function that "wraps" three objects into one structure that can then be passed to the pthread\_create had to be designed. Figure 8.4 illustrated the source code.

```

1. void * startRoutine(void *args_p) {

2. pthread_mutex_lock(&thread_lock);// Avoid problems with scheduling

3. struct argStructType *args = (struct argStructType *) args_p;

4. args->behaviour(args->this_ptr, args->argc, args->argv);

5. free(args_p);

6. pthread_mutex_unlock(&thread_lock); // Unlock mutex

7. return ((void *) 1);

8. }

```

# Figure 8.4 The wrapper function used to pass three parameters to the function run inside of a POSIX thread.

Figure 8.5 shows the function void component\_stop(void \* this\_ptr). It is used for stopping components. This action is possible by calling stop inside of a component to stop this component or stop(sender) to stop a component instanced sender.

```

1. void component_stop(void * this_ptr) {

2. struct IComponent_data *t = (struct IComponent_data*) this_ptr;

3. t->stopped = 1;

4. }

```

Figure 8.5 The function for stopping Insense components.

Let us take a look at now familiar Insense program "Hello" as an example of how components are handled by the Insense runtime. The program was extended and two calls to "stop" were added, for the purposes of demonstration.

```

type IHello is interface (out string output)

type IPrinter is interface (in string input)

component Hello presents IHello {

msg = "Hello World n"

constructor() { }

behaviour {

send msg on output

stop

}

}

component Printer presents IPrinter {

msg = ""

constructor() { }

behaviour {

receive msg from input

printString(msg)

stop

}

}

hello = new Hello()

1.component_create for Hello

printer = new Printer()

2.component_create for Printer

connect hello.output to printer.input

3.component_stop for Hello, after

1 run of behaviour

4.component_stop for Printer,

after 1 run of behaviour

```

(a)

(b)

Figure 8.6 (a): "Hello" program that illustrates management of components. (b): timeline of calls of functions dealing with management of Insense components during execution of the "Hello" program.

Figure 8.6 shows the program along with a timeline of calls to functions that create and stop components, which are outlined above. Each use of the new keyword (e.g. hello = new

Hello()) in Insense code, once compiled and run, results in a call to the component\_create function.

As stated above, the stop keyword is called twice in the program, each call is done in the end of the first run through the behaviour function. These calls result in the function component\_stop being called, which terminate execution of components.

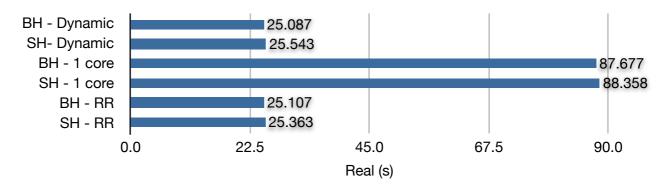

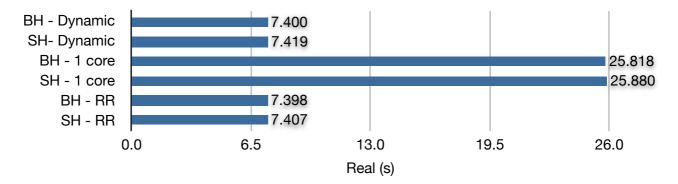

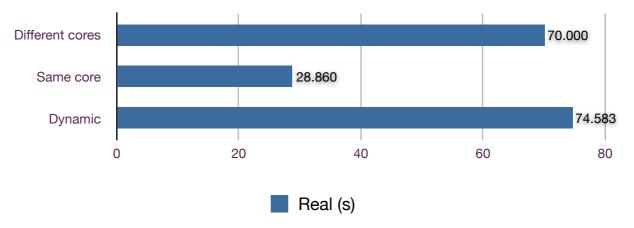

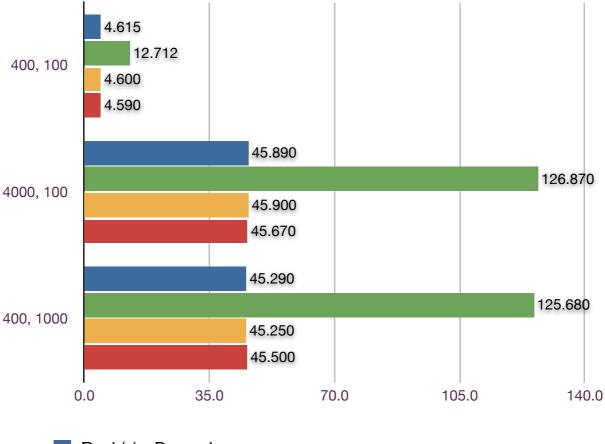

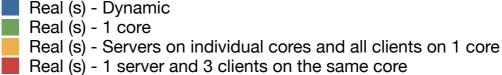

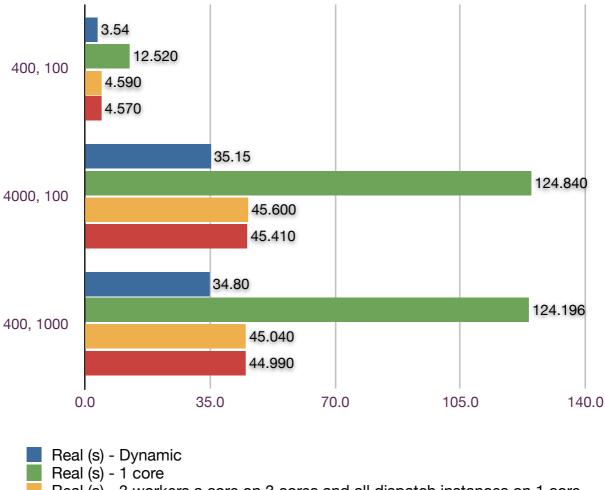

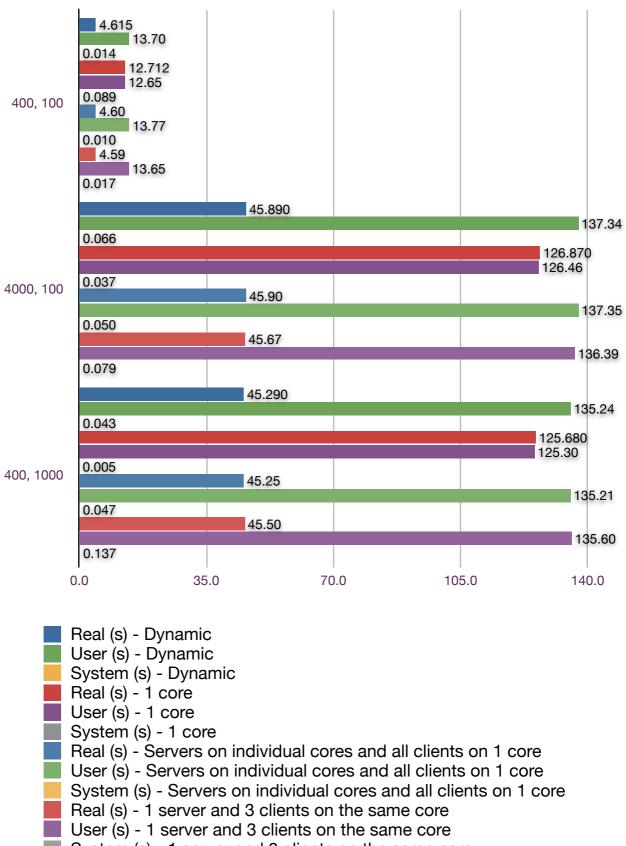

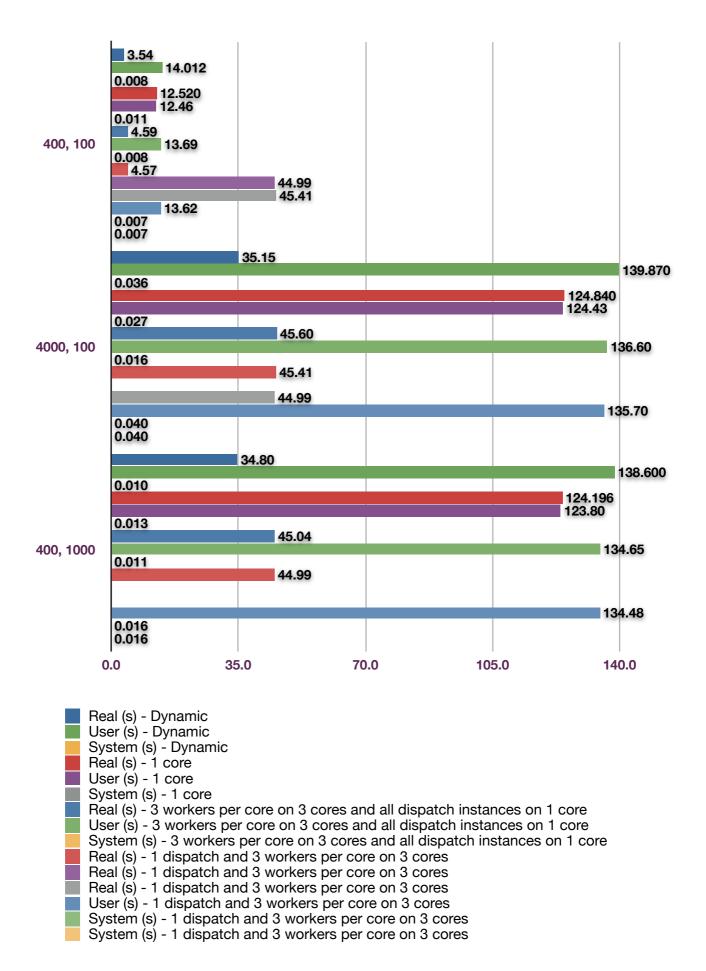

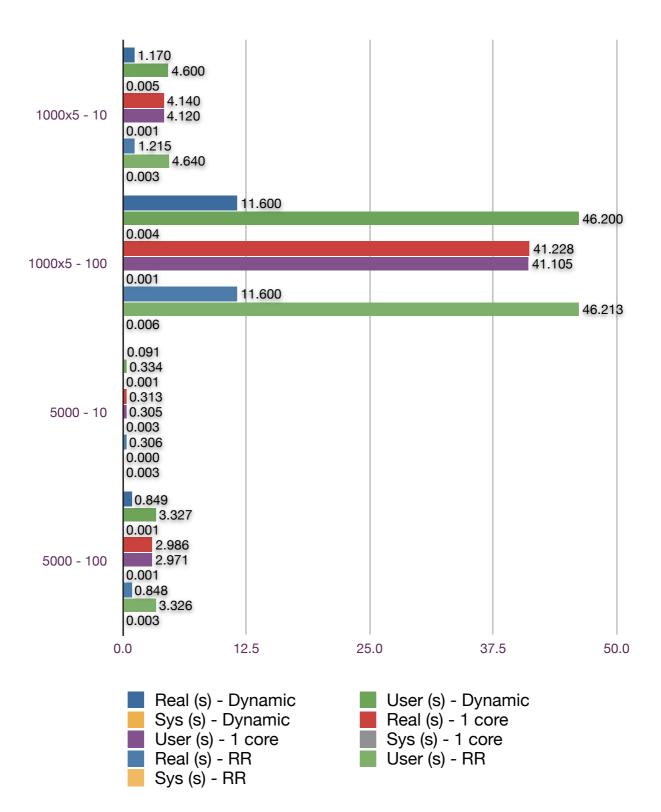

# 8.1.2 Arrays